## 1. 特性

● 频段: 200MHz~5000MHz

● 支持 TDD 和 FDD

● 可调谐通道带宽: 12 kHz 至 100 MHz

● 双通道接收器: 6 路差分或 12 路单端输入

● 出色的接收器灵敏度, 噪声系数为 4 dB

● RX 增益控制:

◆ 实时监控和控制信号用于手动增益

◆ 独立的自动增益控制

● 双通道发射器: 4 路差分输出

● TX 功率最大调节范围: 48dB

TX EVM: ≤- 40 dB

● TX 噪声: <-157 dBm/Hz 本底噪声

● TX 监控器: 动态范围≥40 dB, 精度=1 dB

● 集成小数 N 分频频率合成器

● 多器件同步

● CMOS/LVDS 数字接口

## 2. 主要应用

● 通用软件无线电系统

● 毫微微蜂窝/微微蜂窝/微蜂窝基站

● 多功能智能终端

● 点对点通信系统

## 3. 概述

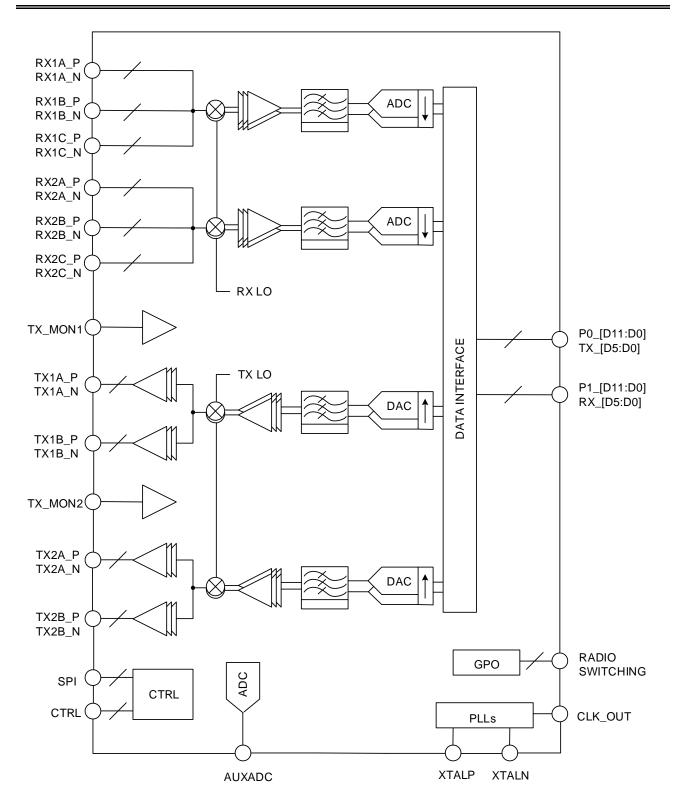

GC0802 是一款高性能、高集成度的超宽带 SDR 收发机,可广泛应用于几乎所有现代化数字无线通信系统。能够支持的频率范围为 200MHz 到 5000MHz,可配置射频带宽能够支持 12KHz 到 100MHz 的范围。

该器件集成了 12bit 的模数转换器 ADC 和 12bit 的数模转换器 DAC。内置可编程模拟滤波器,支持最小 0.7MHz 带宽的模拟低通滤波器以及 TX 最大 50MHz 带宽的模拟低通滤波器,RX 最大 50MHz 的模拟低通滤波器。混频器和锁相环也都集成在芯片内部,并且发射部分集成有驱动级放大器,可以输出 7dBm 以上单音信号。

GC0802 采用直接变频架构,可实现高的调制精度和超低的噪声。该芯片具有镜像抑制校准,本振泄露校准,发射功率监控,杂散抑制以及接收通道增益校准等功能。并且包含有多芯片同步功能,适用于多芯片联合使用的场景,如MIMO。芯片寄存器读写控制采用标准的四线 SPI。GC0802采用 10 mm × 10 mm、 144 引脚芯片级球栅阵列封装(CSP\_BGA)。

图 1 GC0802 系统框图

## 目 录

| 1.  | 特性      | 1  |

|-----|---------|----|

|     |         |    |

| ۷.  | 主要应用    | 1  |

| 3.  | 概述      | 1  |

| 4.  | 产品技术规格  | 4  |

| 5.  | 封装及引脚定义 | 5  |

| 6.  | 技术规格    | 12 |

| 7.  | 工作原理    | 30 |

| 8.  | 修订记录    | 37 |

| 9.  | 订购信息    | 37 |

| 10. | 免责说明    | 38 |

## 4. 产品技术规格

## 4.1 绝对最大额定值

| 参数                   | 绝对值范围                      |

|----------------------|----------------------------|

| VDDx 至 VSSx          | -0.3V~ +1.5V               |

| VDD_INTERFACE 至 VSSx | -0.3V~ +2.7V               |

| VDD_GPO 至 VSSx       | -0.3V~ +3.3V               |

| 逻辑输入和输出至 VSSx        | -0.3V 至 VDD_INTERFACE+0.3V |

| 输入电流至除电源引脚外的任何引脚     | ±10mA                      |

| RF 输入(峰值功率)          | 2.5dBm                     |

| TX 监控器输入功率           | 9dBm                       |

| 最大结温(TJMAX)          | 110°C                      |

| 工作环境温度范围             | -40~85°C                   |

| 存储环境温度范围             | -65~150°C                  |

表 1

#### 4.2 推荐工作条件

| 参数            | 推荐值                            |

|---------------|--------------------------------|

| VDDx          | +1.3V (实际可以接受范围是 1.3V-1.5V 之间) |

| VDD_GPO       | +3.3V                          |

| VDD_INTERFACE | +2.5V                          |

| 工作环境温度        | -40~85°C                       |

表 2

## 4.3 热阻参数

| Package Type       | θJΑ  | θЈВ  | θЈС  | 单位   |

|--------------------|------|------|------|------|

| 144-Ball (CSP-BGA) | 37.5 | 24.4 | 22.5 | °C/W |

表 3

## 4.4 回流温度曲线

GC0802 回流温度曲线依据的是 JEDEC JESD20 器件标准。最大回流温度为 260℃。

#### 4.5 ESD 警告

#### ESD(静电放电)敏感器件

带电器件和电路板可能会在没有察觉的情况下放电。尽管本产品具有专利或专有保护电路,但在遇到高能量 ESD 时,器件可能会损坏。因此,应当采取适当的 ESD 防范措施,以避免器件性能下降或功能丧失。

注:超出上述绝对最大额定值可能会导致器件永久性损坏。这只是额定最值,并不能以这些条件或者在任何其它超出本技术规范操作章节中所示规格的条件下,推断器件能 否正常工作。长期在绝对最大额定值条件下工作会影响器件的可靠性。

## 5. 封装及引脚定义

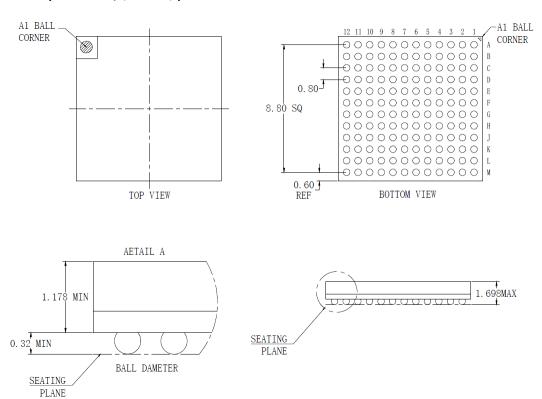

## 5.1 外形尺寸说明(图示尺寸单位:毫米)

图 2 144 引脚芯片级封装球栅阵列

## 5.2 引脚定义说明

|   | 1                | 2               | 3                      | 4                       | 5                   | 6                       | 7                       | 8                  | 9                      | 10                | 11                  | 12                |

|---|------------------|-----------------|------------------------|-------------------------|---------------------|-------------------------|-------------------------|--------------------|------------------------|-------------------|---------------------|-------------------|

| A | RX2A_N           | RX2A_P          | TX2_EXT_D<br>AC_Q_Iout | TX2_EXT_D<br>AC_Q_IOutB | TX_MON2             | TX2_EXT_D<br>AC_I_Iout  | TX2A_P                  | TX2A_N             | TX2B_P                 | TX2B_N            | PADT2P<br>(AUXADC2) | TX_EXT_<br>LO_IN  |

| В | VSSA             | VSSA            | PAD_RX2IF<br>QP        | GP0_3                   | GP0_2               | GP0_1                   | GP0_0                   | VDD_GPO            | VDD1P3_RF              | NC                | NC                  | VSSA              |

| C | RX2B_P           | VSSA            | PAD_RX2IF<br>QN        | TEST/<br>ENABLE         | CTRL_IN0            | CTRL_IN1                | TX2_EXT_D<br>AC_I_IOutB | VSSA               | VSSA                   | VSSA              | VSSA                | VSSA              |

| D | RX2B_N           | VDD 1P3_<br>TX2 | AVDD13_<br>ADD A2      | CTRL_OUT0               | CTRL_IN3            | CTRL_IN2                | P0_D9/<br>TX_D4_P       | P0_D7/<br>TX_D3_P  | P0_D5/<br>TX_D2_P      | P0_D3/<br>TX_D1_P | P0_D1/<br>TX_D0_P   | VSSD              |

| E | RX2C_P           | VDD1P3_RX       | NC                     | CTRL_OUT1               | CTRL_OUT2           | CTRL_OUT3               | P0_D11/<br>TX_D5_P      | P0_D8/<br>TX_D4_N  | P0_D6/<br>TX_D3_N      | P0_D4/<br>TX_D2_N | P0_D2/<br>TX_D1_N   | P0_D0/<br>TX_D0_N |

| F | RX2C_N           | VDD1P3_RX       | VSSA                   | CTRL_OUT6               | CTRL_OUT5           | CTRL_OUT4               | VSSD                    | P0_D10/<br>TX_D5_N | VSSD                   | FB_CLK_P          | VSSD                | VDDD1P3_<br>DIG   |

| G | RX_EXT_<br>LO_IN | PAD_RX2IFI<br>P | PAD_RX2IFI<br>N        | CTRL_OUT7               | EN_AGC              | ENABLE                  | RX_<br>FRAME_N          | RX_<br>FRAME_P     | TX_<br>FRAME_P         | FB_CLK_N          | DATA_<br>CLK_P      | VSSD              |

| Н | RX1C_N           | PAD_RX1IFI<br>P | PAD_RX1IFI<br>N        | TXNRX                   | SYNC_IN             | VSSA                    | VSSD                    | P1_D11/<br>RX_D5_P | TX_<br>FRAME_N         | VSSD              | DATA_<br>CLK_N      | VDD_<br>INTERFACE |

| J | RX1C_P           | VSSA            | AVDD13_<br>ADDA1       | SPI_DI                  | SPI_CLK             | CLK_OUT                 | P1_D10/<br>RX_D5_N      | P1_D9/<br>RX_D4_P  | P1_D7/<br>RX_D3_P      | P1_D5/<br>RX_D2_P | P1_D3/<br>RX_D1_P   | P1_D1/<br>RX_D0_P |

| K | RX1B_N           | VSSA            | VDD 1P3_<br>TX1        | AVDD13<br>_LFCK         | RESETB              | SPI_ENB                 | P1_D8/<br>RX_D4_N       | P1_D6/<br>RX_D3_N  | P1_D4/<br>RX_D2_N      | P1_D2/<br>RX_D1_N | P1_D0/<br>RX_D0_N   | VSSD              |

| L | RX1B_P           | VSSA            | PAD_RX1IF<br>QN        | RBIAS                   | PADT1P<br>(AUXADC1) | SPI_DO                  | TX1_EXT_D<br>AC_I_IOutB | VSSA               | TX1_EXT_D<br>AC_I_Iout | VSSA              | VSSA                | VSSA              |

| M | RX1A_N           | RX1A_P          | PAD_RX1IF<br>QP        | TX1_EXT_D<br>AC_Q_Iout  | TX_MON1             | TX1_EXT_D<br>AC_Q_IOutB | TX1A_P                  | TX1A_N             | TX1B_P                 | TX1B_N            | XTALP               | XTALN             |

| 引脚编号                                                          | 类型  | 引脚名称                                                                  | 说明                                                                                                                                                                                                         |  |  |  |

|---------------------------------------------------------------|-----|-----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| A1,A2                                                         | I   | RX2A_N, RX2A_P                                                        | 接收通道 2 差分输入 A,每个引脚也可以作为单端输入;若未使用此引脚,请接隔直电容到地                                                                                                                                                               |  |  |  |

| A3,A4                                                         | 0   | TX2_EXT_DAC_Q_lout, TX2_EXT_DAC_Q_lOutB                               | 发射通道 2 DAC Q 路差分输出,不用时请接地                                                                                                                                                                                  |  |  |  |

| A5                                                            | I   | TX_MON2                                                               | 发射通道 2 功率监控输入;若未使用此引脚,请接隔<br>直电容到地                                                                                                                                                                         |  |  |  |

| A6,C7                                                         | 0   | TX2_EXT_DAC_I_lout TX2_EXT_DAC_I_OutB                                 | 发射通道 2 DAC I 路差分输出,不用时请接地                                                                                                                                                                                  |  |  |  |

| A7,A8                                                         | 0   | TX2A_P, TX2A_N                                                        | 发射通道 2 差分输出 A,不用请悬空                                                                                                                                                                                        |  |  |  |

| A9,A10                                                        | 0   | TX2B_P, TX2B_N                                                        | 发射通道 2 差分输出 B,不用请悬空                                                                                                                                                                                        |  |  |  |

| A11                                                           | 0   | PADT2P<br>(AUXADC2)                                                   | 用于 CH2 测试使用,引出可以看 CH2 模拟信号; 也可以用于 AUXADC; 若未使用此引脚,请接地                                                                                                                                                      |  |  |  |

| A12                                                           | I   | TX_EXT_LO_IN                                                          | 外部发射 LO 输入; 若未使用此引脚, 请接地                                                                                                                                                                                   |  |  |  |

| B1,B2,B12,C2, C8 to<br>C12,F3,H6,J2,K2,L2,<br>L8,L10,L11, L12 | 1   | VSSA                                                                  | 模拟地                                                                                                                                                                                                        |  |  |  |

| B3,C3                                                         | 0   | PAD_RX2IFQP<br>PAD_RX2IFQN                                            | 接收通道 2 中频差分 Q 路輸出,不用时请悬空                                                                                                                                                                                   |  |  |  |

| B4 to B7                                                      | 0   | GPO_3 to GPO_0                                                        | 支持 3.3V 通用输出                                                                                                                                                                                               |  |  |  |

| B8                                                            | 1   | VDD_GPO                                                               | GPO 3.3V 供电; 若不使用时接到 3.3V 或者悬空                                                                                                                                                                             |  |  |  |

| B9                                                            | 1   | VDD1P3_RF                                                             | RF 1.3V 电源输入                                                                                                                                                                                               |  |  |  |

| B10                                                           | NC  | NC                                                                    | 悬空即可                                                                                                                                                                                                       |  |  |  |

| B11                                                           | NC  | NC                                                                    | 悬空即可                                                                                                                                                                                                       |  |  |  |

| C1,D1                                                         | I   | RX2B_P, RX2B_N                                                        | 接收通道 2 差分输入 B,每个引脚也可以作为单端输入; 若未使用此引脚,请接隔直电容到地                                                                                                                                                              |  |  |  |

| C4                                                            | 1   | TEST/ENABLE                                                           | 测试输入; 正常工作时,将该引脚接地                                                                                                                                                                                         |  |  |  |

| C5,C6,D5,D6                                                   | 1   | CTRL_IN0 至 CTRL_IN3                                                   | 控制输入; 用于手动 RX 增益和 TX 衰减控制                                                                                                                                                                                  |  |  |  |

| D2                                                            | 1   | VDD1P3_TX2                                                            | TX2 1.3V 电源输入,连接至 D3                                                                                                                                                                                       |  |  |  |

| D3                                                            | 1   | AVDD13_ADDA2                                                          | ADC2/DAC2 1.3V 电源输入                                                                                                                                                                                        |  |  |  |

| D4,E4 至 E6,F4 至<br>F6,G4                                      | 0   | CTRL_OUT0,CTRL_OUT1 至<br>CTRL_OUT3,CTRL_OUT6 至<br>CTRL_OUT4,CTRL_OUT7 | 控制输出; 这些引脚是多功能输出,具有可编程功能                                                                                                                                                                                   |  |  |  |

| D7                                                            | 1/0 | P0_D9/TX_D4_P                                                         | 数字数据端口 PO/发射差分输入总线。这是双功能引脚。对于 PO_D9,它充当 12 位双向并行 CMOS 电平数据端口 0 的一部分。或者,在 FDD 模式下该引脚(TX_D4_P)也可作为 LVDS 6 位 TX 差分输入总线(带内部 LVDS 端子)的一部分;在 TDD 模式下,该引脚(TX_D4_P)也可作为 LVDS 12 位 TX 或者 RX 差分输入总线(带内部 LVDS 端子)的一部分 |  |  |  |

| D8 I/O P0_D7/TX_D3_P                                          |     | P0_D7/TX_D3_P<br>表 4 引脚定 <sup>3</sup>                                 | 数字数据端口 PO/发射差分输入总线。这是双功能是脚。对于 PO_D7,它充当 12 位双向并行 CMOS 电型数据端口 0 的一部分。或者,在 FDD 模式下该引脚(TX_D3_P)也可作为 LVDS 6 位 TX 差分输入总线(带序部 LVDS 端子)的一部分;在 TDD 模式下,该引脚(TX_D3_P)也可作为 LVDS 12 位 TX 或者 RX 差分输入总线(带内部 LVDS 端子)的一部分 |  |  |  |

表 4 引脚定义

| 引脚编号                                 | 类型  | 引脚名称           | 说明                                                                                                                                                                                                         |

|--------------------------------------|-----|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D9                                   | I/O | P0_D5/TX_D2_P  | 数字数据端口 P0/发射差分输入总线。这是双功能引脚。对于P0_D5,它充当 12 位双向并行 CMOS 电平数据端口 0 的一部分。或者,在 FDD 模式下该引脚(TX_D2_P)也可作为 LVDS 6 位 TX 差分输入总线(带内部 LVDS 端子)的一部分;在 TDD 模式下,该引脚(TX_D2_P)也可作为 LVDS 12 位 TX 或者 RX 差分输入总线(带内部 LVDS 端子)的一部分  |

| D10                                  | I/O | P0_D3/TX_D1_P  | 数字数据端口 P0/发射差分输入总线。这是双功能引脚。对于P0_D3,它充当 12 位双向并行 CMOS 电平数据端口 0 的一部分。或者,在 FDD 模式下该引脚(TX_D1_P)也可作为 LVDS 6 位 TX 差分输入总线(带内部 LVDS 端子)的一部分;在 TDD 模式下,该引脚(TX_D1_P)也可作为 LVDS 12 位 TX 或者 RX 差分输入总线(带内部 LVDS 端子)的一部分  |

| D11                                  | I/O | PO_D1/TX_DO_P  | 数字数据端口 P0/发射差分输入总线。这是双功能引脚。对于P0_D1,它充当 12 位双向并行 CMOS 电平数据端口 0 的一部分。或者,在 FDD 模式下该引脚(TX_D0_P)也可作为 LVDS 6 位 TX 差分输入总线(带内部 LVDS 端子)的一部分;在 TDD 模式下,该引脚(TX_D0_P)也可作为 LVDS 12 位 TX 或者 RX 差分输入总线(带内部 LVDS 端子)的一部分  |

| D12, F7, F9,F11,<br>G12, H7,H10, K12 | 1   | VSSD           | 数字地                                                                                                                                                                                                        |

| E1, F1                               | 1   | RX2C_P, RX2C_N | 接收通道 2 差分输入 C,每个引脚也可以作为单端输入;若未使用此引脚,请接隔直电容到地                                                                                                                                                               |

| E2                                   | 1   | VDD1P3_RX      | 接收1.3 V 电源输入。                                                                                                                                                                                              |

| E3                                   | NC  | NC             | 悬空即可                                                                                                                                                                                                       |

| E7                                   | I/O | P0_D11/TX_D5_P | 数字数据端口 P0/发射差分输入总线。这是双功能引脚。对于P0_D11,它充当 12 位双向并行 CMOS 电平数据端口 0 的一部分。或者,在 FDD 模式下该引脚(TX_D5_P)也可作为 LVDS 6 位 TX 差分输入总线(带内部 LVDS 端子)的一部分;在 TDD 模式下,该引脚(TX_D5_P)也可作为 LVDS 12 位 TX 或者 RX 差分输入总线(带内部 LVDS 端子)的一部分 |

| E8                                   | I/O | P0_D8/TX_D4_N  | 数字数据端口 PO/发射差分输入总线。这是双功能引脚。对于PO_D8,它充当 12 位双向并行 CMOS 电平数据端口 0 的一部分。或者,在 FDD 模式下该引脚(TX_D4_N)也可作为 LVDS 6 位 TX 差分输入总线(带内部 LVDS 端子)的一部分;在 TDD 模式下,该引脚(TX_D4_N)也可作为 LVDS 12 位 TX 或者 RX 差分输入总线(带内部 LVDS 端子)的一部分  |

| E9                                   | I/O | P0_D6/TX_D3_N  | 数字数据端口 PO/发射差分输入总线。这是双功能引脚。对于PO_D6,它充当 12 位双向并行 CMOS 电平数据端口 0 的一部分。或者,在 FDD 模式下该引脚(TX_D3_N)也可作为 LVDS 6 位 TX 差分输入总线(带内部 LVDS 端子)的一部分;在 TDD 模式下,该引脚(TX_D3_N)也可作为 LVDS 12 位 TX 或者 RX 差分输入总线(带内部 LVDS 端子)的一部分  |

| E10                                  | I/O | P0_D4/TX_D2_N  | 数字数据端口 PO/发射差分输入总线。这是双功能引脚。对于PO_D4,它充当 12 位双向并行 CMOS 电平数据端口 0 的一部分。或者,在 FDD 模式下该引脚(TX_D2_N)也可作为 LVDS 6 位 TX 差分输入总线(带内部 LVDS 端子)的一部分;在 TDD 模式下,该引脚(TX_D2_N)也可作为 LVDS 12 位 TX 或者 RX 差分输入总线(带内部 LVDS 端子)的一部分  |

表 5 引脚定义(续)

| 引脚编号     | 类型  | 引脚名称                       | 说明                                                                                                                                                                                                         |

|----------|-----|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| E11      | 1/0 | P0_D2/TX_D1_N              | 数字数据端口 P0/发射差分输入总线。这是双功能引脚。对于P0_D2,它充当 12 位双向并行 CMOS 电平数据端口 0 的一部分。或者,在 FDD 模式下该引脚(TX_D1_N)也可作为 LVDS 6 位 TX 差分输入总线(带内部 LVDS 端子)的一部分;在 TDD 模式下,该引脚(TX_D1_N)也可作为 LVDS 12 位 TX 或者 RX 差分输入总线(带内部 LVDS 端子)的一部分  |

| E12      | 1/0 | P0_D0/TX_D0_N              | 数字数据端口 P0/发射差分输入总线。这是双功能引脚。对于P0_D0,它充当 12 位双向并行 CMOS 电平数据端口 0 的一部分。或者,在 FDD 模式下该引脚(TX_D0_N)也可作为 LVDS 6 位 TX 差分输入总线(带内部 LVDS 端子)的一部分;在 TDD 模式下,该引脚(TX_D0_N)也可作为 LVDS 12 位 TX 或者 RX 差分输入总线(带内部 LVDS 端子)的一部分  |

| F2       | 1   | VDDA1P3_RX                 | 接收 VCO LDO 1.3 V 电源输入                                                                                                                                                                                      |

| F8       | 1/0 | P0_D10/TX_D5_N             | 数字数据端口 PO/发射差分输入总线。这是双功能引脚。对于PO_D10,它充当 12 位双向并行 CMOS 电平数据端口 0 的一部分。或者,在 FDD 模式下该引脚(TX_D5_N)也可作为 LVDS 6 位 TX 差分输入总线(带内部 LVDS 端子)的一部分;在 TDD 模式下,该引脚(TX_D5_N)也可作为 LVDS 12 位 TX 或者 RX 差分输入总线(带内部 LVDS 端子)的一部分 |

| F10, G10 | 1   | FB_CLK_P, FB_CLK_N         | 反馈时钟。这些引脚接收作为 TX 数据时钟的 FB_CLK 信号。在 CMOS 模式中,以 FB_CLK_P 为输入,将 FB_CLK_N 接地。                                                                                                                                  |

| F12      | I   | VDD1P3_DIG                 | 1.3 V 数字电源输入                                                                                                                                                                                               |

| G1       | 1   | RX_EXT_LO_IN               | 外部接收 LO 输入; 若未使用此引脚, 则将其接地                                                                                                                                                                                 |

| G2,G3    | 0   | PAD_RX2IFIP<br>PAD_RX2IFIN | 接收通道 2 中频差分   路輸出,不用时请悬空                                                                                                                                                                                   |

| G5       | 1   | EN_AGC                     | 用于自动增益控制(AGC)的手动控制输入                                                                                                                                                                                       |

| G6       | 1   | ENABLE                     | 控制输入。该引脚使器件在各种运行状态之间移动                                                                                                                                                                                     |

| G7,G8    | 0   | RX_FRAME_N, RX_FRAME_P     | 接收数字数据帧输出信号。这些引脚发射 RX_FRAME 信号,用于指示 RX 输出数据是否有效。在 CMOS 模式下,以 RX_FRAME_P 为输出,使 RX_FRAME_N 保持断开状态                                                                                                            |

| G9, H9   | I   | TX_FRAME_P, TX_FRAME_N     | 发射数字数据帧输入信号。这些引脚接收用于指示 TX 数据何时有效的 TX_FRAME 信 号 。 在 CMOS 模 式 中 , 以 TX_FRAME_P 为 输 入 , 将 TX_FRAME_N 接地                                                                                                       |

| G11, H11 | 0   | DATA_CLK_P, DATA_CLK_N     | 接收数据时钟输出。这些引脚发射 DATA_CLK 信号, BBP 用这些信号为 RX 数据提供时钟。在 CMOS 模式下,以 DATA_CLK_P 为输出,使 DATA_CLK_N 保持断开状态。                                                                                                         |

| H1, J1   | 1   | RX1C_N, RX1C_P             | 接收通道 1 差分输入 C,每个引脚也可以作为单端输入;若未使用此引脚,请接隔直电容到地                                                                                                                                                               |

| H2,H3    | 0   | PAD_RX1IFIP<br>PAD_RX1IFIN | 接收通道 1 中频差分   路输出,不用时请悬空                                                                                                                                                                                   |

| H4       | I   | TXNRX                      | 使能状态机控制信号。该引脚控制数据端口总线方向。逻辑低电平选择 RX 方向,逻辑高电平选择 TX 方向                                                                                                                                                        |

| H5       | I   | SYNC_IN                    | 用于同步多个 GC0802 器件之间数字时钟的输入;若未使用此引脚,则将其接地                                                                                                                                                                    |

| H8       | 1/0 | P1_D11/RX_D5_P             | 数字数据端口 P1/接收差分输出总线。这是双功能引脚。对于P1_D11,它充当 12 位双向并行 CMOS 电平数据端口 1 的一部分。或者,在 FDD 模式下该引脚(RX_D5_P)也可作为 LVDS 6 位 RX 差分输出总线(带内部 LVDS 端子)的一部分;在 TDD 模式下,该引脚(RX_D5_P)也可作为 LVDS 12 位 TX 或者 RX 差分输入总线(带内部 LVDS 端子)的一部分 |

| H12      | 1   | VDD_INTERFACE              | 数字 I/O 引脚,1.8 V 至 2.5 V 电源                                                                                                                                                                                 |

表 6 引脚定义 (续 2)

| 引脚编号   | 类型  | 引脚名称           | 说明                                                                                                                                                                                                             |

|--------|-----|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| J3     | 1   | AVDD13_ADDA1   | ADC1/DAC1 1.3V 电源输入                                                                                                                                                                                            |

| ]4     | 1   | SPI_DI         | SPI 串行数据输入                                                                                                                                                                                                     |

| J5     | 1   | SPI CLK        | SPI 时钟输入                                                                                                                                                                                                       |

| J6     | 0   | CLK_OUT        | 输出时钟。可将该引脚配置为输出缓冲版外部输入时钟 DCXO,或者输出分频版内部 ADC_CLK                                                                                                                                                                |

| J7     | 1/0 | P1_D10/RX_D5_N | 数字数据端口 P1/接收差分输出总线。这是双功能引脚。对于P1_D10, 它充当 12 位双向并行 CMOS 电平数据端口 1 的一部分。或者, 在 FDD 模式下该引脚(RX_D5_N)也可作为 LVDS 6 位 RX 差分输出总线(带内部 LVDS 端子)的一部分; 在 TDD 模式下, 该引脚(RX_D5_N)也可作为 LVDS 12 位 TX 或者 RX 差分输入总线(带内部 LVDS 端子)的一部分 |

| J8     | 1/0 | P1_D9/RX_D4_P  | 数字数据端口 P1/接收差分输出总线。这是双功能引脚。对于 P1_D9,它充当 12 位双向并行 CMOS 电平数据端口 1 的一部分。或者,在 FDD模式下该引脚(RX_D4_P)也可作为 LVDS 6 位 RX 差分输出总线(带内部 LVDS 端子)的一部分;在 TDD 模式下,该引脚(RX_D4_P)也可作为 LVDS 12 位 TX 或者 RX 差分输入总线(带内部 LVDS 端子)的一部分      |

| J9     | 1/0 | P1_D7/RX_D3_P  | 数字数据端口 P1/接收差分输出总线。这是双功能引脚。对于 P1_D7,它充当 12 位双向并行 CMOS 电平数据端口 1 的一部分。或者,在 FDD模式下该引脚(RX_D3_P)也可作为 LVDS 6 位 RX 差分输出总线(带内部 LVDS 端子)的一部分;在 TDD 模式下,该引脚(RX_D3_P)也可作为 LVDS 12 位 TX 或者 RX 差分输入总线(带内部 LVDS 端子)的一部分      |

| J10    | 1/0 | P1_D5/RX_D2_P  | 数字数据端口 P1/接收差分输出总线。这是双功能引脚。对于 P1_D5,它充当 12 位双向并行 CMOS 电平数据端口 1 的一部分。或者,在 FDD模式下该引脚(RX_D2_P)也可作为 LVDS 6 位 RX 差分输出总线(带内部 LVDS 端子)的一部分;在 TDD 模式下,该引脚(RX_D2_P)也可作为 LVDS 12 位 TX 或者 RX 差分输入总线(带内部 LVDS 端子)的一部分      |

| J11    | 1/0 | P1_D3/RX_D1_P  | 数字数据端口 P1/接收差分输出总线。这是双功能引脚。对于 P1_D3,它充当 12 位双向并行 CMOS 电平数据端口 1 的一部分。或者,在 FDD模式下该引脚(RX_D1_P)也可作为 LVDS 6 位 RX 差分输出总线(带内部 LVDS 端子)的一部分;在 TDD 模式下,该引脚(RX_D1_P)也可作为 LVDS 12 位 TX 或者 RX 差分输入总线(带内部 LVDS 端子)的一部分      |

| J12    | 1/0 | P1_D1/RX_D0_P  | 数字数据端口 P1/接收差分输出总线。这是双功能引脚。对于 P1_D1,它充当 12 位双向并行 CMOS 电平数据端口 1 的一部分。或者,在 FDD模式下该引脚(RX_D0_P)也可作为 LVDS 6 位 RX 差分输出总线(带内部 LVDS 端子)的一部分;在 TDD 模式下,该引脚(RX_D0_P)也可作为 LVDS 12 位 TX 或者 RX 差分输入总线(带内部 LVDS 端子)的一部分      |

| K1, L1 | I   | RX1B_N, RX1B_P | 接收通道 1 差分输入 B,每个引脚也可以作为单端输入;若未使用此引脚,请接隔直电容到地                                                                                                                                                                   |

| K3     | I   | VDD1P3_TX1     | TX1 1.3 V 电源输入                                                                                                                                                                                                 |

| K4     | 1   | AVDD13_LFCK    | SYSPLL/XO 1.3 V 电源输入                                                                                                                                                                                           |

| K5     | 1   | RESETB         | 异步复位。逻辑低电平复位器件                                                                                                                                                                                                 |

| K6     | 1   | SPI_ENB        | SPI 使能输入。将该引脚设为逻辑低电平,以使能 SPI 总线                                                                                                                                                                                |

| K7     | 1/0 | P1_D8/RX_D4_N  | 数字数据端口 P1/接收差分输出总线。这是双功能引脚。对于 P1_D8,它充当 12 位双向并行 CMOS 电平数据端口 1 的一部分。或者,在 FDD 模式下该引脚(RX_D4_N)也可作为 LVDS 6 位 RX 差分输出总线(带内部 LVDS 端子)的一部分;在 TDD 模式下,该引脚(RX_D4_N)也可作为 LVDS 12 位 TX 或者 RX 差分输入总线(带内部 LVDS 端子)的一部分     |

| K8     | 1/0 | P1_D6/RX_D3_N  | 数字数据端口 P1/接收差分输出总线。这是双功能引脚。对于 P1_D6,它充当 12 位双向并行 CMOS 电平数据端口 1 的一部分。或者,在 FDD模式下该引脚(RX_D3_N)也可作为 LVDS 6 位 RX 差分输出总线(带内部 LVDS 端子)的一部分;在 TDD 模式下,该引脚(RX_D3_N)也可作为 LVDS 12 位 TX 或者 RX 差分输入总线(带内部 LVDS 端子)的一部分      |

表 7 引脚定义(续3)

| 引脚编号    | 类型  | 引脚名称                                      | 说明                                                                                                                                                                                                         |

|---------|-----|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| K9      | 1/0 | P1_D4/RX_D2_N                             | 数字数据端口 P1/接收差分输出总线。这是双功能引脚。对于 P1_D4,它充当 12 位双向并行 CMOS 电平数据端口 1 的一部分。或者,在 FDD 模式下该引脚(RX_D2_N)也可作为 LVDS 6 位 RX 差分输出总线(带内部 LVDS 端子)的一部分;在 TDD 模式下,该引脚(RX_D2_N)也可作为 LVDS 12 位 TX 或者 RX 差分输入总线(带内部 LVDS 端子)的一部分 |

| K10     | 1/0 | P1_D2/RX_D1_N                             | 数字数据端口 P1/接收差分输出总线。这是双功能引脚。对于 P1_D2,它充当 12 位双向并行 CMOS 电平数据端口 1 的一部分。或者,在 FDD 模式下该引脚(RX_D1_N)也可作为 LVDS 6 位 RX 差分输出总线(带内部 LVDS 端子)的一部分;在 TDD 模式下,该引脚(RX_D1_N)也可作为 LVDS 12 位 TX 或者 RX 差分输入总线(带内部 LVDS 端子)的一部分 |

| K11     | 1/0 | P1_D0/RX_D0_N                             | 数字数据端口 P1/接收差分输出总线。这是双功能引脚。对于 P1_D0,它充当 12 位双向并行 CMOS 电平数据端口 1 的一部分。或者,在 FDD 模式下该引脚(RX_D0_N)也可作为 LVDS 6 位 RX 差分输出总线(带内部 LVDS 端子)的一部分;在 TDD 模式下,该引脚(RX_D0_N)也可作为 LVDS 12 位 TX 或者 RX 差分输入总线(带内部 LVDS 端子)的一部分 |

| L3,M3   | 0   | PAD_RX1IFQN<br>PAD_RX1IFQP                | 接收通道 1 中频差分 Q 路輸出,不用时请悬空                                                                                                                                                                                   |

| L4      | 1   | RBIAS                                     | 偏置输入参考。通过一个 14.3 kΩ (1%容差)电阻将此引脚接地                                                                                                                                                                         |

| L5      | 0   | PADTIP<br>(AUXADC1)                       | 用于 CH1 测试引脚,引出可以看 CH1 模拟信号。也可以用于 AUXADC。 若未使用此引脚,请接地                                                                                                                                                       |

| L6      | 0   | SPI_DO                                    | 4 线模式的 SPI 串行数据输出                                                                                                                                                                                          |

| L7,L9   | 0   | TX1_EXT_DAC_I_IOutB<br>TX1_EXT_DAC_I_lout | 发射通道 1 DAC I 路差分输出,不用时请接地                                                                                                                                                                                  |

| M1,M2   | 1   | RX1A_N, RX1A_P                            | 接收通道 1 差分输入 A,每个引脚也可以作为单端输入;若未使用此引脚,请接隔直电容到地                                                                                                                                                               |

| M4,M6   | 0   | TX1_EXT_DAC_Q_lout<br>TX1_EXT_DAC_Q_lOutB | 发射通道 1 DAC Q 路差分输出,不用时请接地                                                                                                                                                                                  |

| M5      | 1   | TX_MON1                                   | 发射通道 1 功率监控输入;若未使用此引脚,请接隔<br>直电容到地                                                                                                                                                                         |

| M7,M8   | 0   | TX1A_P, TX1A_N                            | 发射通道 1 差分输出 A,不用时请悬空                                                                                                                                                                                       |

| M9,M10  | 0   | TX1B_P, TX1B_N                            | 发射通道 1 差分输出 B,不用时请悬空                                                                                                                                                                                       |

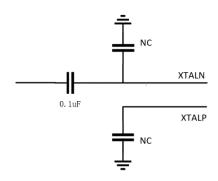

| M11,M12 | I   | XTALP, XTALN<br>素 g 引脚定义 (4               | 参考频率晶振连接。使用晶振时,将其连接于这两个引脚之间。使用外部时钟源时,将其连接至 XTALN,使 XTALP 保持断开                                                                                                                                              |

表 8 引脚定义(续4)

## 6. 技术规格

## 6.1 接收器指标

除非另有说明,电气特性在 VDD\_GPO = 3.3 V, VDD\_INTERFACE = 2.5 V,所有其他 VDDx 引脚= 1.3 V, TA = 25°C 下测得。

| 参数           | 标识   | 最小值   | 典型值       | 最大值  | 单位  | 测试条件                         |

|--------------|------|-------|-----------|------|-----|------------------------------|

| 接收器中心频率      |      | 200   |           | 5000 | MHz |                              |

| 支持射频带宽       |      | 0.012 |           | 100  | MHz |                              |

| 模拟增益最小值      |      |       | 8         |      | dB  |                              |

| 模拟增益最大值      |      | 48    | 50        | 52   | dB  | 50dB@2.4GHz                  |

| 模拟增益步进       |      |       | 1         |      | dB  |                              |

| 数字增益最小值      |      |       | 0         |      | dB  |                              |

| 数字增益最大值      |      |       | 50        |      | dB  |                              |

| 数字增益步进       |      |       | 0.25      |      | dB  |                              |

| 接收器 700MHz   |      |       |           |      |     |                              |

| 噪声系数         | NF   |       | 2.7       |      | dB  | 最大 RX 增益                     |

| 三阶输入交调载点     | IIP3 |       | -2        |      | dBm | 最大 RX 增益                     |

| 二阶输入交调载点     | IIP2 |       | 52        |      | dBm | 最大 RX 增益                     |

| 本振(LO)泄漏     |      |       | -77       |      | dBm | RX 前端输入                      |

| 调制精度(EVM)    |      |       | -40.5     |      | dB  | 30.72 MHz 参考时钟; LTE20M, QPSK |

| 输入 S11       |      |       | -10       |      | dB  |                              |

| RX1 至 RX2 隔离 |      |       | 80        |      | dB  | RX1A 至 RX2A                  |

| RX2 至 RX1 隔离 |      |       | 80        |      | dB  | RX2A 至 RX1A                  |

| 接收器 2400MHz  |      |       |           |      |     |                              |

| 噪声系数         | NF   |       | 4.3       |      | dB  | 最大 RX 增益                     |

| 三阶输入交调载点     | IIP3 |       | -3        |      | dBm | 最大 RX 增益                     |

| 二阶输入交调载点     | IIP2 |       | 43.5      |      | dBm | 最大 RX 增益                     |

| 本振(LO)泄漏     |      |       | -62       |      | dBm | RX 前端输入                      |

| 调制精度(EVM)    |      |       | -39       |      | dB  | 30.72 MHz 参考时钟; LTE20M, QPSK |

| 输入 S11       |      |       | -10       |      | dB  |                              |

| RX1 至 RX2 隔离 |      |       | 70        |      | dB  | RX1A 至 RX2A                  |

| RX2 至 RX1 隔离 |      |       | 70        |      | dB  | RX2A 至 RX1A                  |

| 接收器 3600MHz  |      |       |           |      |     |                              |

| 噪声系数         | NF   |       | 4.4       |      | dB  | 最大 RX 增益                     |

| 三阶输入交调载点     | IIP3 |       | -3        |      | dBm | 最大 RX 增益                     |

| 二阶输入交调载点     | IIP2 |       | 38        |      | dBm | 最大 RX 增益                     |

| 本振(LO)泄漏     |      |       | -62       |      | dBm | RX 前端输入                      |

| 调制精度(EVM)    |      |       | -37.5     |      | dB  | 30.72 MHz 参考时钟; LTE20M, QPSK |

| 输入 S11       |      |       | -10       |      | dB  |                              |

| RX1 至 RX2 隔离 |      |       | 70        |      | dB  | RX1A 至 RX2A                  |

| RX2 至 RX1 隔离 |      |       | 70 主 0 拉ル |      | dB  | RX2A 至 RX1A                  |

表 9 接收器指标

## 6.2 发射器指标

除非另有说明,电气特性在 VDD\_GPO = 3.3 V, VDD\_INTERFACE = 2.5 V, 所有其他 VDDx 引脚= 1.3 V, TA = 25°C 下测得。

| 参数            | 标识       | 最小值   | 典型值   | 最大值  | 单位     | 测试条件                         |

|---------------|----------|-------|-------|------|--------|------------------------------|

| 发射器中心频率       |          | 200   |       | 5000 | MHz    |                              |

| 支持射频带宽        |          | 0.012 |       | 100  | MHz    |                              |

| 模拟功率控制范围      |          | 46    | 48    | 50   | dB     | 48dB@2.4GHz                  |

| 模拟功率控制步进      |          |       | 1     |      | dB     |                              |

| 数字功率控制范围      |          |       | 50    |      | dB     |                              |

| 数字功率控制步进      |          |       | 0.125 |      | dB     |                              |

| TX 监控器(TX_MON | 1/TX_MON | N2)   |       |      | L      |                              |

| 最大输入电平        |          |       | 0     |      | dBm    | 最大输入线性电平                     |

| 动态范围          |          |       | 41    |      | dB     |                              |

| 准确度           |          |       | 1     |      | dB     |                              |

| 发射器 700MHz    | -I       |       |       |      | I      | ,                            |

| 输出 S22        |          |       | -10   |      | dB     |                              |

| 最大输出功率        |          |       | 4     |      | dBm    | 单音                           |

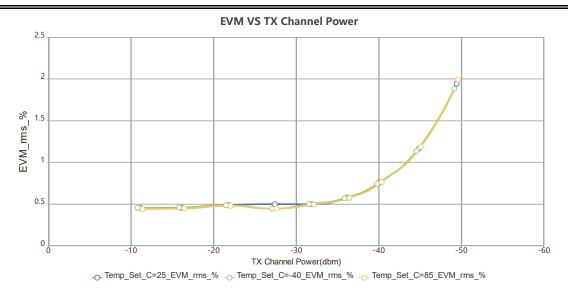

| 调制精度(EVM)     |          |       | -47.5 |      | dB     | 30.72 MHz 参考时钟; LTE20M, QPSK |

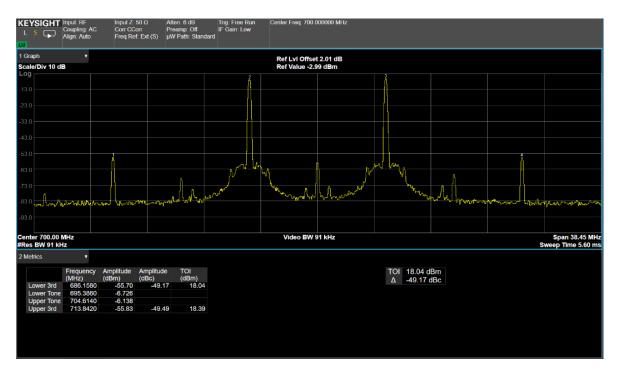

| 三阶输出交调载点      | OIP3     |       | 18    |      | dBm    |                              |

| 载波泄漏          |          |       | -61   |      | dBc    | 0 dB 衰减                      |

| 载波泄漏          |          |       | -40   |      | dBc    | 40 dB 衰减                     |

| 镜像抑制          |          |       | -75   |      | dBc    |                              |

| 本底噪声          |          |       | -157  |      | dBm/Hz | 90MHz 偏移                     |

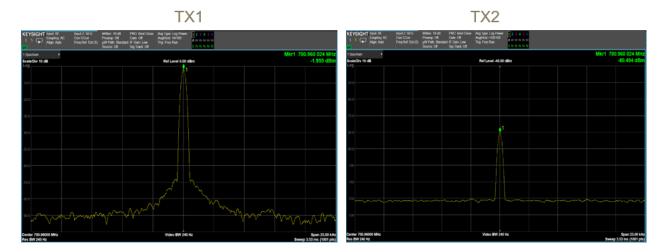

|               |          |       | 78    |      | dB     |                              |

| 隔离度 TX2 至 TX1 |          |       | 78    |      | dB     |                              |

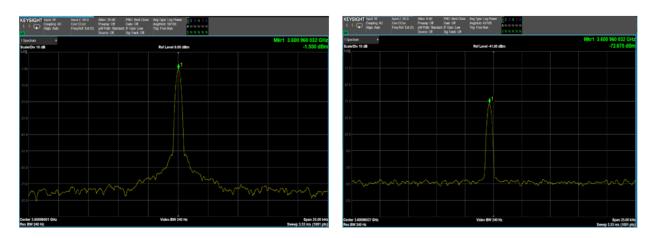

| 发射器 2400MHz   |          |       |       |      |        | L                            |

| 输出 S22        |          |       | -10   |      | dB     |                              |

| 最大输出功率        |          |       | 5     |      | dBm    | 単音                           |

| 调制精度(EVM)     |          |       | -43   |      | dB     | 30.72 MHz 参考时钟; LTE20M, QPSK |

| 三阶输出交调载点      | OIP3     |       | 18    |      | dBm    | -                            |

| 载波泄漏          |          |       | -61   |      | dBc    | 0 dB 衰减                      |

| 载波泄漏          |          |       | -40   |      | dBc    | 40 dB 衰减                     |

| 镜像抑制          |          |       | -70   |      | dBc    |                              |

| 本底噪声          |          |       | -156  |      | dBm/Hz | 90MHz 偏移                     |

| 隔离度 TX1 至 TX2 |          |       | 78    |      | dB     |                              |

|               |          |       | 78    |      | dB     |                              |

| 发射器 3600MHz   | ı        |       |       |      |        |                              |

| 输出 S22        |          |       | -10   |      | dB     |                              |

| 最大输出功率        |          |       | 5     |      | dBm    | 単音                           |

| 调制精度(EVM)     |          |       | -41   |      | dB     | 30.72 MHz 参考时钟; LTE20M, QPSK |

| 三阶输出交调载点      | OIP3     |       | 17.5  |      | dBm    |                              |

| 载波泄漏          |          |       | -57   |      | dBc    | 0 dB 衰减                      |

| 载波泄漏          |          |       | -36   |      | dBc    | 40 dB 衰减                     |

| 镜像抑制          |          |       | -68   |      | dBc    |                              |

| 本底噪声          |          |       | -154  |      | dBm/Hz | 90MHz 偏移                     |

| 隔离度 TX1 至 TX2 |          |       | 70    |      | dB     |                              |

| 隔离度 TX2 至 TX1 |  |  | 70 |  | dB |  |

|---------------|--|--|----|--|----|--|

|---------------|--|--|----|--|----|--|

表 10 发射器指标

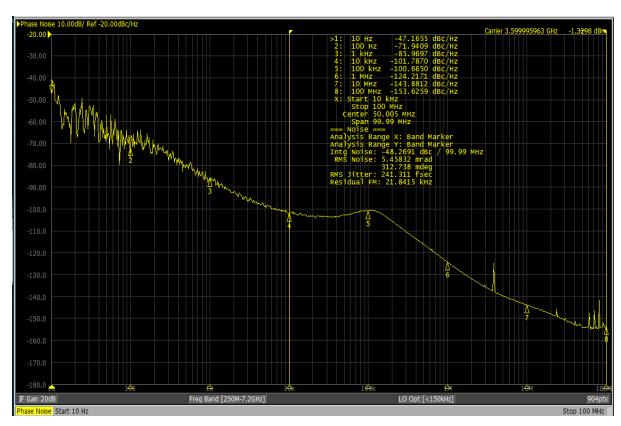

## 6.3 频综指标

除非另有说明,电气特性在 VDD\_GPO = 3.3 V, VDD\_INTERFACE = 2.5 V,所有其他 VDDx 引脚= 1.3 V, TA = 25°C 下测得。

| 参数                  | 最小值  | 典型值   | 最大值    | 单位   | 测试条件    |  |  |  |  |

|---------------------|------|-------|--------|------|---------|--|--|--|--|

| 参考时钟                |      |       |        |      |         |  |  |  |  |

| 参考时钟(晶振或者外<br>部振荡器) | 12.6 |       | 122.88 | MHz  |         |  |  |  |  |

| 本振频率合成器             |      |       |        |      |         |  |  |  |  |

| 本振分辨率               |      | 2.4   |        | Hz   |         |  |  |  |  |

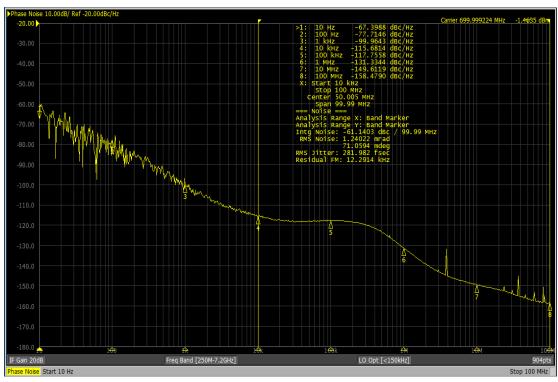

|                     |      | 0.071 |        | °rms | 700MHz  |  |  |  |  |

| 积分相位噪声              |      | 0.238 |        | °rms | 2400MHz |  |  |  |  |

| (10KHz~100MHz)      |      | 0.312 |        | °rms | 3600MHz |  |  |  |  |

| 基带频率合成器             |      |       |        |      |         |  |  |  |  |

| 输出频率范围              | 1800 |       | 3600   | MHz  |         |  |  |  |  |

表 11 频综指标

## 6.4 功耗指标

除非另有说明,电气特性在 VDD\_GPO = 3.3 V, VDD\_INTERFACE = 2.5 V,所有其他 VDDx 引脚= 1.3 V, TA = 25°C 下测得。

| 参数               | 最小值 | 典型值  | 最大值 | 单位 | 测试条件              |

|------------------|-----|------|-----|----|-------------------|

| 1T1R_LTE20M 功耗   |     | 793  |     | mW | B3 频段 LTE20M FDD  |

| 2T2R_LTE20M 功耗   |     | 1180 |     | mW | B3 频段 LTE20M FDD  |

| 1T1R_100M_FDD 功耗 |     | 1059 |     | mW | N41 频段 NR100M FDD |

| 1T_NR100_TDD 功耗  |     | 555  |     | mW | N41 频段 NR100M TDD |

| 1R_NR100_TDD 功耗  |     | 750  |     | mW | N41 频段 NR100M TDD |

| 2T_NR100_TDD 功耗  |     | 1153 |     | mW | N41 频段 NR100M TDD |

| 2R_NR100_TDD 功耗  |     | 1227 |     | mW | N41 频段 NR100M TDD |

| Sleep mode 功耗    |     | 0.14 |     | mW | Sleep Mode        |

表 12 功耗指标

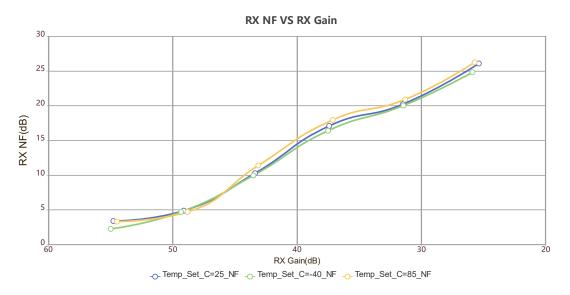

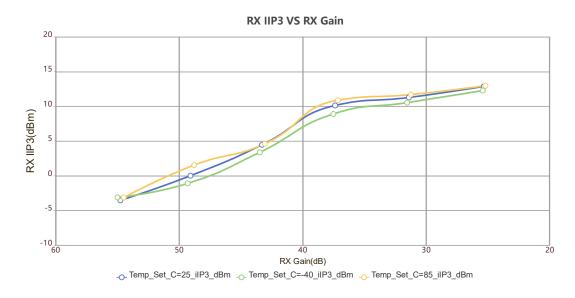

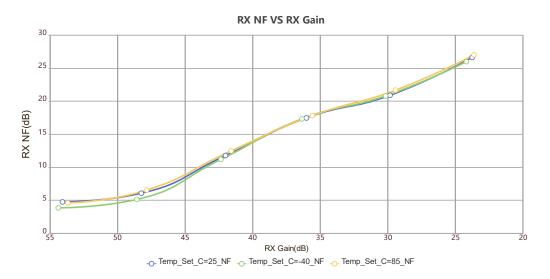

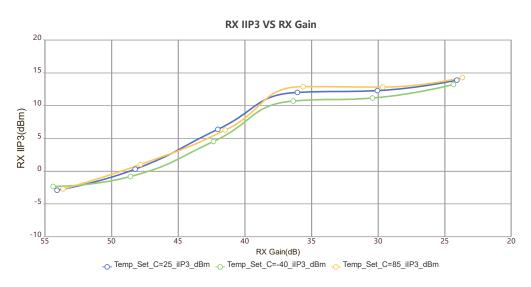

## 6.5 典型性能参数

700M 频段

图 3 RX NF 与 RX Gain 的关系(RX LO=700M)

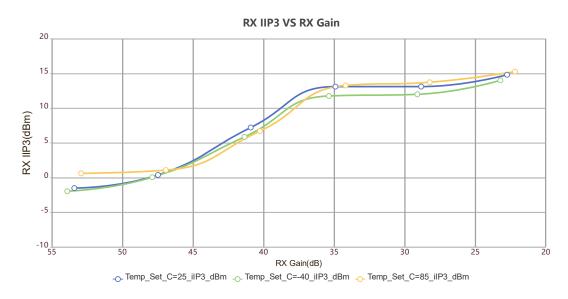

图 4 RX IIP3 与 RX Gain 的关系(RX LO=700M)

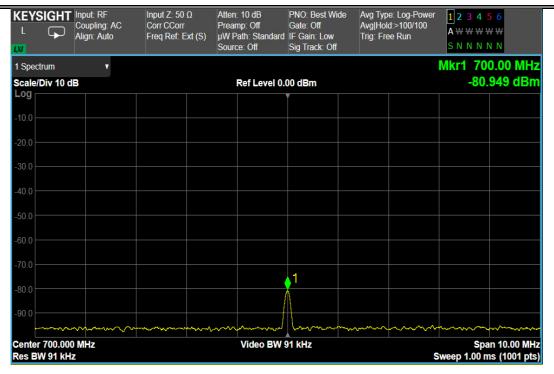

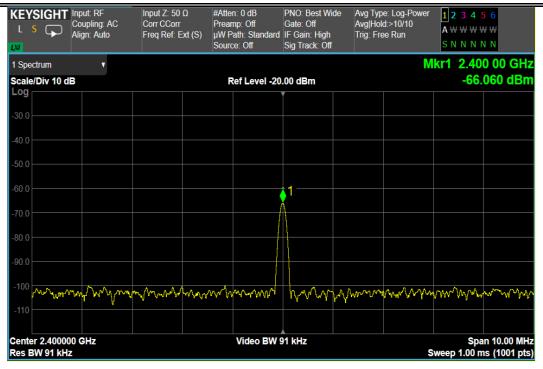

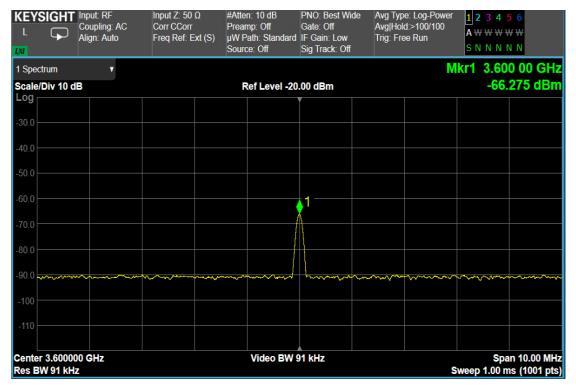

图 5 RX LO leakage (RX LO=700M)

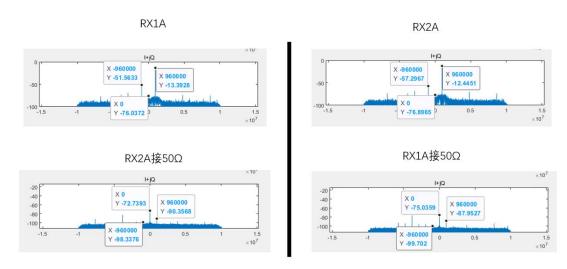

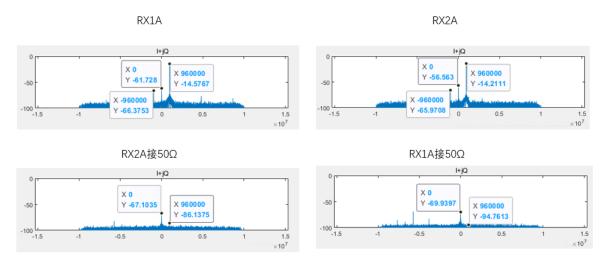

图 6 RX 隔离度 (RX LO=700M, 单位 dBFs)

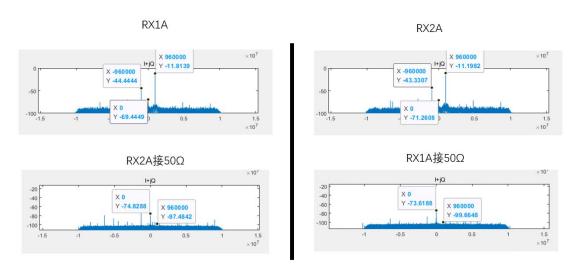

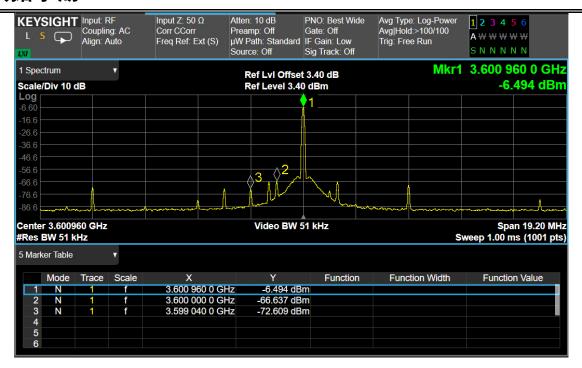

图 7 TX QEC&LOL (TX LO=700M,0dB 衰减)

图 8 TX QEC&LOL (TX LO=700M,40dB 衰减)

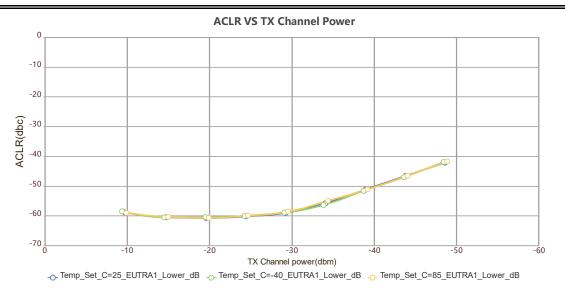

图 9 TX ACLR 与 TX Channel Power 的关系 (TX LO=700M)

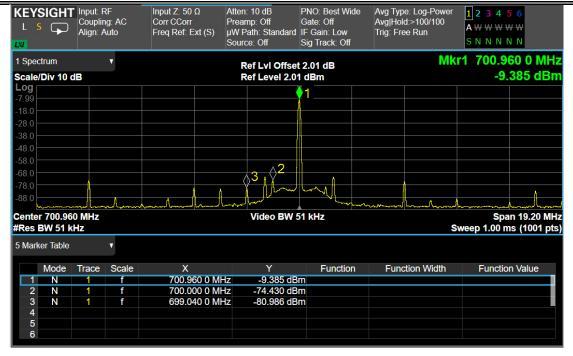

图 10 TX OIP3 (TX LO=700M)

图 11 TX EVM 与 TX Channel Power 的关系 (TX LO=700M)

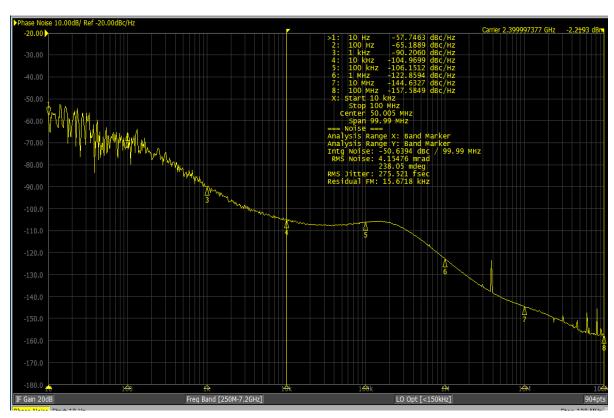

图 12 相位噪声 (TX LO=700M)

图 13 TX1 至 TX2 隔离度 (TX LO=700M)

## 2.4G 频段

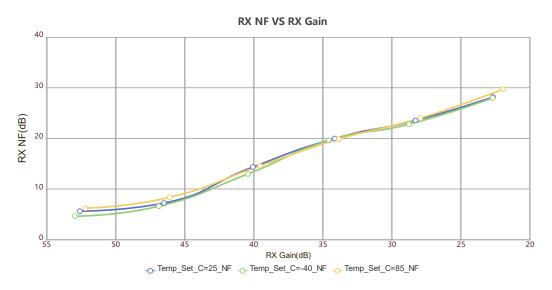

图 14 RX NF 与 RX Gain 的关系(RX LO=2400M)

图 15 RX IIP3 与 RX Gain 的关系 (RX LO=2400M)

图 16 RX LO leakage(RX LO=2400M)

图 17 RX 隔离度 (RX LO=2400M, 单位 dBFs)

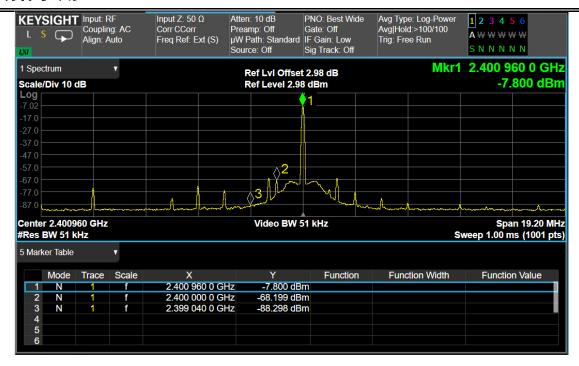

图 18 TX QEC&LOL (TX LO=2400M,0dB 衰减)

图 19 TX QEC&LOL (TX LO=2400M,40dB 衰减)

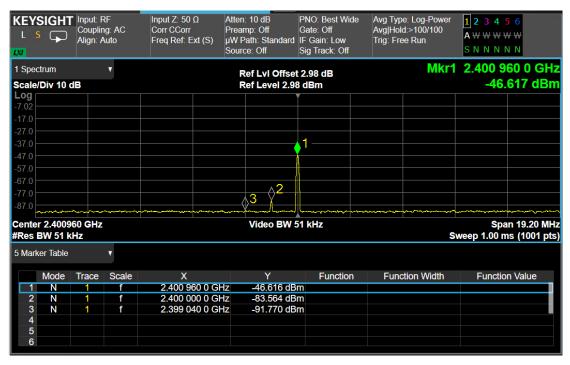

图 20 TX ACLR 与 TX Channel Power 的关系 (TX LO=2400M)

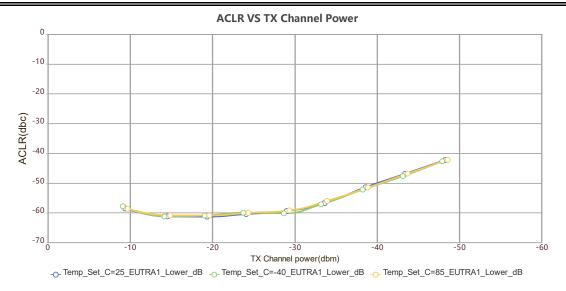

图 21 TX OIP3 (TX LO=2400M)

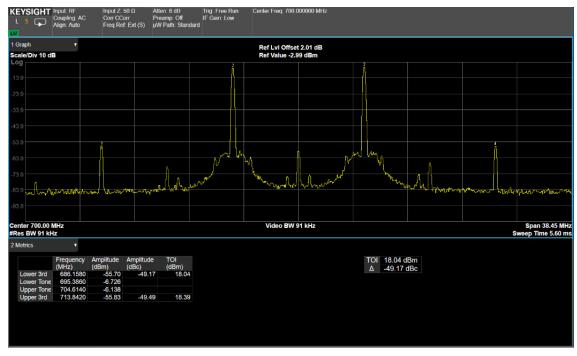

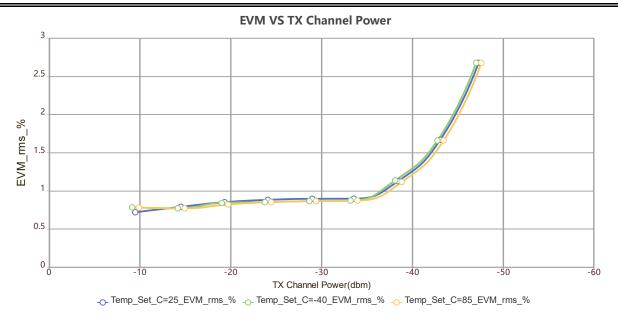

图 22 TX EVM 与 TX Channel Power 的关系 (TX LO=2400M)

图 23 TX 相位噪声 (TX LO=2400M)

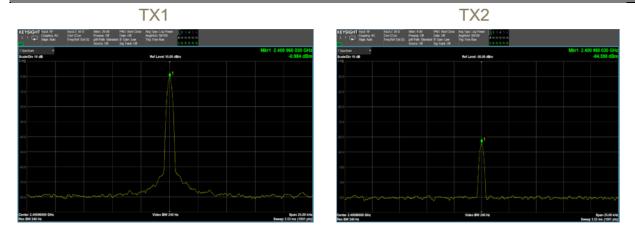

图 24 TX1 至 TX2 隔离度 (TX LO=2400M)

## 3.6G 频段

图 25 RX NF 与 RX Gain 的关系(RX LO=3600M)

图 26 RX IIP3 与 RX Gain 的关系 (RX LO=3600M)

图 27 RX LO leakage(RX LO=3600M)

图 28 RX 隔离度 (RX LO=3600M, 单位 dBFs)

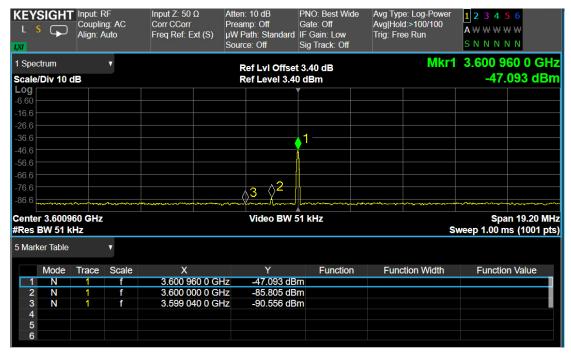

图 29 TX QEC&LOL (TX LO=3600M,0dB 衰减)

图 30 TX QEC&LOL (TX LO=3600M,40dB 衰减)

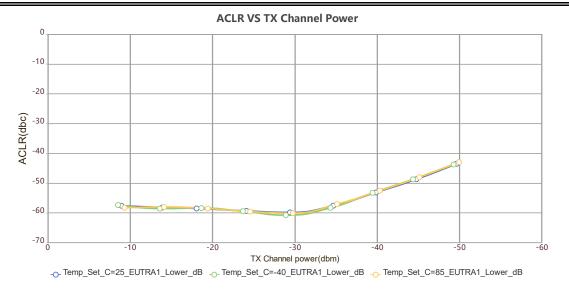

图 31 TX ACLR 与 TX Channel Power 的关系 (TX LO=3600M)

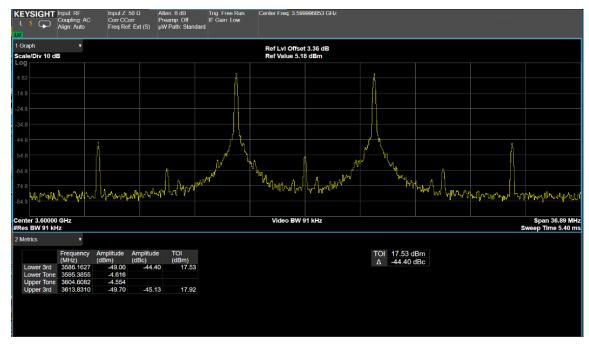

图 32 TX OIP3 (TX LO=3600M)

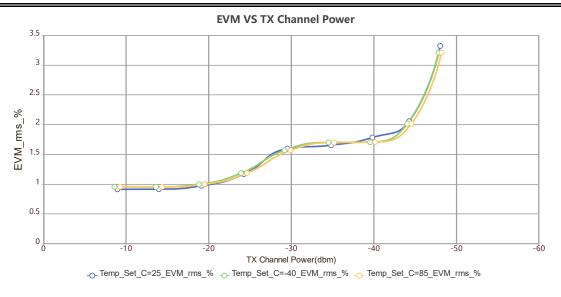

图 33 TX EVM 与 TX Channel Power 的关系 (TX LO=3600M)

图 34 相位噪声 (TX LO=3600M)

图 35 TX1 至 TX2 隔离度 (TX LO=3600M)

## 7. 工作原理

#### 7.1 一般特性

GC0802 是一款高集成度的射频(RF)收发器,能够配置用于广泛应用,在单个器件中集成了提供所有收发器功能的所有必要 RF、混合信号和数字模块。可编程能力使这款宽带收发器可以适用于多种通信标准,包括频分双工(FDD)和时分双工(TDD)系统。此外,这种可编程能力还允许通过单通道 12 位并行数据端口、双通道 12 位并行数据端口或 12 位低电压差分信令(LVDS)接口,与各种基带处理器(BBP)相连接。

GC0802 还提供了自我校准和自动增益控制(AGC)系统,可以在多种温度和输入信号条件下维持高性能水平。

#### 7.2 接收器

接收器部分含有所有必要模块,用于接收 RF 信号并将其转换成可供 BBP 使用的数字数据。有两个独立控制的通道,可以接收来自不同源的信号,使器件可以用于多输入、多输出(MIMO)系统,同时还可共享一个通用频率合成器。每个通道都有三个差分输入或者六个单端输入,可以多路复用至信号链,使 GC0802 可以用于搭载多个天线输入的分集系统。接收器是一个直接变频系统,含有混频器和频带整形滤波器,该滤波器可以将接收到的信号下变频为基带,以便进行数字化。依据预编程增益指数映射,可实现增益控制,该映射将增益分配于各模块之间,从而实现各电平下的性能优化。这可以通过在快速或慢速模式下使能内部 AGC 来实现,也可通过手动增益控制来实现,使 BBP 可以根据需要调整增益。此外,各个通道还拥有独立的 RSSI 测量功能、直流失调跟踪功能和进行自我校准的所有必要电路。接收器包括 12 位 SAR ADC 和可调采样速率,可以从收到的信号产生数据流。数字化信号可以通过一系列抽取滤波器和一个完全可编程的 128 抽头 FIR 滤波器(带有额外的抽取设置)进一步调理。各个数字滤波器模块的采样速率可以通过更改抽取系数来进行调整,从而产生需要的输出数据速率。

#### 7.3 发射器

发射器部分含有两个相同的、独立控制的通道,提供了所有必要的数字处理、混合信号和 RF 模块,可以实现一个直接变频系统,同时共用一个通用型频率合成器。从 BBP 收到的数字数据通过一个不带插值选项的完全可编程 128 抽头 FIR 滤波器。 FIR 输出被发送到一系列插值滤波器,在输出到达 DAC 之前,提供额外的滤波和数据速率插值处理。每个 12 位 DAC 都拥有可调的采样速率。 I 和 Q 通道都馈入 RF 模块以进行上变频。

每个发射通道内置自我校准电路,以支持自动实时调整。发射器模块同时为每个通道提供一个 TX 监控器模块。该模块监控发射器输出,并通过一个未使用的接收器通道将其送回 BBP,以实现信号监控。 TX 监控器模块仅在接收器空闲的 TDD 模式下可用。

### 7.4 时钟输入选项

GC0802 运行时使用的参考时钟输入电平范围是 0.5Vpp - 2.5Vpp, 推荐值是 1.3Vpp, XTALN 单端输入。单端输入时,请在 XTALN 输入端串联一个 0.1uF 电容; XTALP 推荐串联一个电容到地。推荐电路如下图:

参考时钟可由两个不同时钟源提供。第一个选择是使用一个专门的晶振,其频率在 12.6MHz 和 122.88MHz 之间,一般连接于 XTALP 和 XTALN 引脚之间。第二个选择是将一个外部振荡器或时钟分配器件,一般连接至 XTALN 引脚(其中 XTALP 引脚保持断开状态)。如果使用外部振荡器,则频率可在 12.6 MHz 和 122.88 MHz 之间变化。

该参考时钟用于为频率合成器模块提供电源,这些模块在器件内部生成所有数据时钟、采样时钟和本振。利用数字可编程、数字控制晶振(DCXO)功能来调节片内可变电容,则可消除晶振频率误差。该电容可以调谐系统中的晶振频率变化,结果产生精度更高的参考时钟,而所有其他频率就是从这些时钟生成的。该功能也可配合片内温度检测功能使用,以便在正常运行中提供振荡器频率温度补偿。

#### 7.5 频率合成器

#### **RF PLL**

GC0802 含有两个完全相同的频率合成器,用于为 RF 信号路径生成需要的 LO 信号:一个用于接收器,一个用于发射器,并且发射的可以切换给接收使用。锁相环(PLL)频率合成器采用小数 N 设计,融入了完全集成式电压控制振荡器(VCO)和环路滤波器。在 TDD 运行模式下,频率合成器会根据 RX 和 TX 帧的需要开启和关闭。在 FDD 模式下, TX PLL 和 RX PLL 可以同时激活。这些 PLL 不需要外部元件。

#### BB PLL

GC0802 还含有一个基带 PLL 频率合成器, 用于生成所有基带相关时钟信号。这些包括 ADC 和 DAC 采样时钟、DATA\_CLK 信号和所有数据帧信号。该 PLL 的编程频率范围为 1800 MHz 至 3600 MHz, 具体取决于系统的数据速率和采样速率要求。

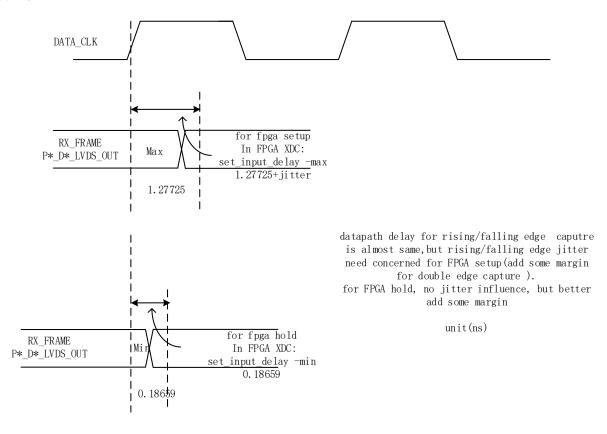

#### 7.6 数字数据接口

GC0802 数据接口采用并行数据端口(P0 和 P1)来在器件和 BBP 之间传输数据。数据端口可以配置为单端 CMOS 格式或差分 LVDS 格式。这两种格式都可以配置为多种方式,以满足数据排序和数据端口连接的系统需求。具体包括单端口数据总线、双端口数据总线、单数据速率、双数据速率和各种数据排序组合,以在适当的时间将来自不同通道的数据传过总线。总线传输是通过简单的硬件握手信令来控制的。两个端口可以工作于双向(TDD)模式或全双工(FDD)模式,在后一种模式下,一半位

数用于发射数据、一半用于接收数据。

接口也可配置为,只将其中一个数据端口用于不需要高数据速率而且倾向于使用较少接口引脚的应用。

#### DATA CLK 信号

RX 数据提供 DATA\_CLK 信号,BBP 可以在接收数据时使用后者。DATA\_CLK 可以设为提供单数据速率(SDR)时序的速率 (其中,数据在各上升时钟沿采样),也可设为提供双数据速率(DDR)时序(其中,同时在上升沿和下降沿捕获数据)。该时序适用于使用单端口或两个端口的运行模式。

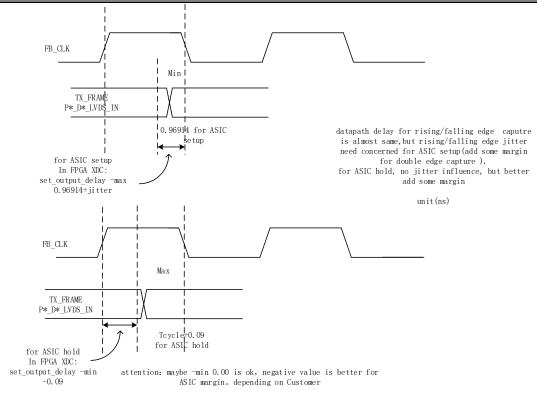

#### FB CLK 信号

对于发射数据,接口以 FB\_CLK 信号作为时序参考。对于突发控制信号,FB\_CLK 允许源与上升沿捕获时序同步,而对于发射信号突发,则允许与上升沿(SDR 模式)或双沿捕获 (DDR 模式 )时序同步。 FB\_CLK 信号必须具有与 DATA\_CLK 的频率和占空比。

#### RX FRAME 信号

每当接收器输出有效数据时,器件都会生成一个 RX\_FRAME 输出信号。该信号有两个模式:电平模式(RX\_FRAME 在数据有效期间保持高电平)和脉冲模式 (RX\_FRAME 以 50%的占空比脉动)。类似地, BBP 必须提供一个 TX\_FRAME 信号,以上升沿来指示有效数据传输的开始。与 RX\_FRAME 相似, TX\_FRAME 信号可能在整个突发过程中保持高电平,或者,可能以 50%的占空比脉动。

图 36 GC080x to FPGA 时序

图 37 FPGA to GC080x 时序

| 参数         | 最小值  | 典型值  | 最大值  | 单位 |

|------------|------|------|------|----|

| 逻辑输入电压范围   | 825  |      | 1575 | mV |

| 逻辑输入差分电压阈值 | -100 |      | 100  | mv |

| 接收差分输入阻抗   |      | 100  |      | Ω  |

| 接收差分电压范围   | 100  | 350  | 600  | mV |

| 逻辑输出电压     |      |      | 1375 | mV |

| 逻辑输出低电压    | 1025 |      |      | mV |

| 逻辑输出差分电压   | 150  |      |      | mV |

| 逻辑输出共模电压   |      | 1200 |      | mV |

表 13 LVDS 参数指标

| 参数                         | Symbol | 最小值   | 典型值 | 最大值  | 单位 |

|----------------------------|--------|-------|-----|------|----|

| DATA_CLK 时钟周期              | Тср    | 4.069 |     |      | ns |

| DATA_CLK 和 FB_CLK 脉冲<br>宽带 | Tmp    | 45%   |     | 55%  | ns |

| TX数据建立至FB_CLK              | Tstx   | 1.25  |     |      | ns |

| TX 数据保持至 FB_CLK            | Thtx   | 0     |     |      | ns |

| DATA_CLK 至数据总线输出<br>延迟     | Tddrx  | 0.18  |     | 1.28 | ns |

| DATA_CLK 至 RX_FRAME 延<br>迟 | Tddrv  | 0.18  |     | 1.28 | ns |

表 14 LVDS 时序指标

## 7.7 使能状态机

GC0802 收发器包括一个使能状态机(ENSM),允许对器件的当前状态进行实时控制。在正常运行过程中,器件可以置于 多种不同状态,包括

- 待机—节能, 频率合成器被禁用

- 休眠—待机.. 所有时钟 BB PLL 被禁用

- TX-TX 信号链被使能

- RX—RX 信号链被使能

- FDD—TX 和 RX 信号链被使能

- 报警--频率合成器被使能

ENSM 有两种可能的控制方法: SPI 控制和引脚控制。

#### SPI 控制模式

在 SPI 控制模式下, 通过写 SPI 寄存器, 从当前状态进入下一状态, 从而实现对 ENSM 的异步控制。SPI 控制被认为与 DATA\_CLK 异步,因为 SPI\_CLK 可能派生自一个不同的参考时钟,而且仍然能正常工作。当不需要对频率合成器进行实时控制时,推荐采用 SPI 控制 ENSM 法。只要 BBIC 能够精确执行 SPI 写操作, SPI 控制就可以用于实时控制。

#### 引脚控制模式

在引脚控制模式下, ENABLE 引脚和 TXNRX 引脚的使能功能允许对当前状态进行实时控制。 ENSM 支持 TDD 或 FDD 运行模式,具体取决于相应 SPI 寄存器的配置。如果 BBIC 有可以实时控制的额外控制输出,允许用一个简单的双线接口来控制器件状态,则建议使用 ENABLE 和 TXNRX 引脚控制方法。为了使 ENSM 的当前状态进入下一状态,可以通过一个脉冲(边沿在内部检测)或电平来 ENABLE 引脚的使能功能。使用脉冲时,其最小脉冲宽度必须为至少两个 FB\_CLK 周期。在电平模式下, ENABLE 和 TXNRX 引脚同样由 GC0802 检测其边沿,而且必须符合相同的最小脉冲宽度要求,即一个 FB\_CLK 周期。在 FDD 模式下, ENABLE 和 TXNRX 引脚必须重新映射,作为实时 RX 和 TX 数据传输控制信号。在该模式下, ENABLE 引脚使能或禁用接收信号路径, TXNRX 引脚使能或禁用发射信号路径。在该模式下, ENSM 将从系统中移除,以便由这些引脚控制所有数据流。

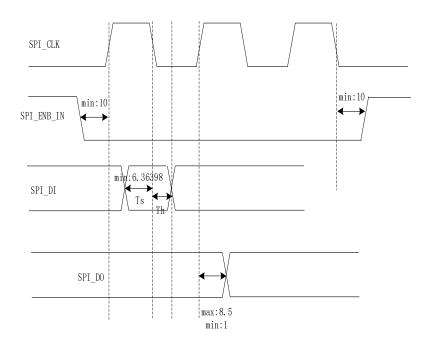

#### 7.8 SPI 接口

GC0802 通过一个串行外设接口(SPI)与 BBP 通信。该接口可以配置为 4 线接口,带有专门的接收和发射端口。该总线允许 BBP 通过一种简单地址数据串行总线协议,设置所有器件控制参数。写命令遵循一种 24 位格式。前 4 位用于设置总线方向和需要传输的字节数。接下来的 12 位数据的写入地址。最后 8 位是将被传输至指定寄存器地址(MSB 至 LSB)的数据。GC0802 还支持 LSB 优先格式,允许命令以 LSB 至 MSB 格式写入。在该模式下,对于多字节写命令,寄存器地址将递增。读命令遵循相似的格式,区别在于,前 16 位在 SPI\_DI 引脚上传输,最后 8 位从 GC0802 中读取,如果是 4 线模式,则在 SPI\_DO 引脚上完成。

单位: ns

Ts: Min 6.36ns

Th: Min 1ns

Tco: 1~8.5ns

图 38 SPI 时序

|                            | 最小值               | 典型值 | 最大值               | 单位 |

|----------------------------|-------------------|-----|-------------------|----|

| 高电平                        | VDD_INTERFACE*0.9 |     | VDD_INTERFACE     | V  |

| 低电平                        | 0                 |     | VDD_INTERFACE*0.1 | V  |

| SPI_CLK 周期                 |                   | 40  |                   | ns |

| SPI_CLK 脉冲宽度               | 25                |     |                   | ns |

| SPI_CLK Rising transition: | 0                 |     | 4                 | ns |

| SPI_CLK Rising transition: | 0                 |     | 4                 | ns |

| SPI_ENB 建立至第一个 SPI_CLK 上升沿 | 10                |     |                   | ns |

| 最后 SPI_CLK 下降沿至 SPI_ENB 保持 | 10                |     |                   | ns |

表 15 SPI 时序

#### 7.9 通用控制引脚

#### 控制输出(CTRL\_OUT[7:0])

GC0802 提供 8 个同步实时输出信号,用作 BBP 的中断。这些输出可以配置为输出一些内部设置和测量值, BBP 在监控 收发器在不同情况下的性能时可以使用这些设置和测量值。控制输出指针寄存器选择将哪些信息输出到这些引脚,而控制输 出使能寄存器则决定 BBP 将激活哪些信号以便监控。用于手动增益模式的信号、校准标志、状态机状态和 ADC 输出都是可以 在这些引脚上监控的部分输出。

#### 控制输入(CTRL\_IN[3:0])

GC0802 提供 4 个边沿检测控制输入引脚。在手动增益模式下, BBP 可以用这些引脚来实时更改增益表索引。在发射模式下, BBP 可以使用两个这些引脚来实时更改发射增益。

#### GPO 引脚(GPO\_3 至 GPO\_0)

GC0802 提供 4 个支持 3.3 V 的通用逻辑输出引脚: GPO\_3、GPO\_2、 GPO\_1 和 GPO\_0。这些引脚可以用于通过 GC0802 SPI 总线控制其他外设器件,比如稳压器、开关等,或者,也可充当内部 GC0802 状态机的从机。

#### 7.10 辅助转化器 AUXADC

GC0802 含有两个辅助 ADC,可以用来监控温度、功率输出等系统功能。转换器为 12 位宽,输入范围为 0 V 至 1 V。使能时, ADC 处于自由运行状态。 SPI 读操作提供在 ADC 输出端锁存的最后值。借助位于 ADC 之前的一个多路复用器,用户可以在 AUXADC 输入引脚与内置温度传感器之间进行选择。AUXADC 不能在初始化的时候或者校准状态以及做 RX peak 检测的时候使用,其他时候都可以使用;

#### 7.11 GC0802的供电

GC0802 必须通过以下三种电源供电:模拟电源(VDDD1P3\_DIG/VDDAx = 1.3 V),接口电源(VDD\_INTERFACE = 2.5 V或者 1.8V)和 GPO 电源(VDD\_GPO = 3.3 V)。对于要求优化噪声性能的应用,建议用低噪声、低压差(LDO)稳压器分离和提供 1.3 V电源。

对于注重电路板空间并且最佳噪声性能不构成绝对要求的应用, 1.3 V 模块电轨可以直接由一个开关提供,并且可以采取一种集成程度更高的电源管理装置(PMU)。

## 8. 修订记录

| 版本    | 日期      | 描述                                                                   |

|-------|---------|----------------------------------------------------------------------|

| 0.1   | 2022/3  | Draft                                                                |

| 0.2   | 2022/9  | 4.2、7.4章节以及B2 pin脚说明部分更新;更新RX端口说明;AUXADC功能更新                         |

| 0.3   | 2022/10 | 5.2章节芯片引脚更新                                                          |

| 0.4   | 2023/02 | 更新AUXADC                                                             |

| 0.4.1 | 2023/02 | 更新了工作带宽是200MHz-5GHz;最小带宽更新至12K;更新第6章题目为"技术规格",增加6.5"典型性能参数"小节,更新图序;  |

| 0.4.2 | 2023/04 | 更新pin脚说明;更新了6.5节测试图;更新了LVDS参数;更新热阻参数;增加订购信息                          |

| 0.4.3 | 2023/05 | 更新6.1接收器参数;更新6.2发射器参数                                                |

| 0.5.0 | 2023/11 | 更新5.1章节芯片封装尺寸图;更新6.3章节频综指标说明;更新5.3章节RX以及TXMON 管脚的说明;删除3线SPI;         |

| 0.5.1 | 2023/12 | 更新6.3章节积分相位噪声参数                                                      |

| 1.0   | 2024/06 | 更新了主要TX,RX,SX的射频指标;更新了B3/C3/L3/M3 PIN脚的定义;更新了B8PIN脚的描述;<br>更新6.5节贴图; |

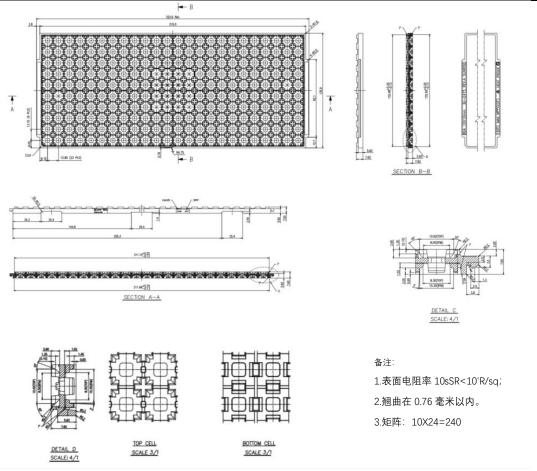

# 9. 订购信息

| 产品型号   | 封装形式                  | 包装方式 | 最小起订量 |

|--------|-----------------------|------|-------|

| GC0802 | GC0802 TFBGA144 10*10 |      | 240   |

|        |                       |      |       |

|        |                       |      |       |

图 39 GC0802 包装信息

## 10. 免责说明

本手册版权归杭州地芯科技有限公司所有,并保留一切权利。未经书面许可,任何单位、组织和个人不得将此文档中的任何部分公开、转载或以其他方式散发给第三方,否则将追究其法律责任。本手册版本将不定期更新,请在使用本产品之前联系本单位销售部门获取本手册的最新版本。用户因未严格按本手册要求保存、使用本产品,致使产品工作异常或损坏,造成任何直接或间接损失,本单位不承担任何责任。用户对本手册有疑问之处请与本单位销售部门联系